Vol. No.4, Issue 07, July 2015

www.ijarse.com

# PULSE WIDTH MODULATION TECHNIQUE FOR DIODE CLAMPED MULTI-LEVEL (THREE & FIVE LEVEL) INVERTER FOR THD ANALYSIS

Akhlakur Rahman<sup>1</sup>, Mr. Jitendra Kumar Garg<sup>2</sup>, Danish Chaudhary<sup>3</sup>

<sup>1</sup>Student, M.Tech, <sup>2</sup>Associate Prof., Department of Electrical & Electronics Engineering, Alfalah University, (India)

<sup>3</sup>Assistant Prof., Department of Electrical & Electronics Engineering, LKCE, Ghaziabad, (India)

#### **ABSTRACT**

The conventional two Level Inverter has many limitations for high voltage and high power application. Multilevel inverter becomes very popular for high voltage and high power application. The multilevel began with the three level converters. The elementary concept of a multilevel converter to achieve higher power to use a series of power semiconductor switches with several lower voltage dc source to perform the power conversion by synthesizing a staircase voltage waveform. However, the output voltage is smoother with a three level converter, in which the output voltage has three possible values. This results in smaller harmonics, but on the other hand it has more components and is more complex to control. In this paper, study of different three level & five level inverter topologies and SPWM technique is explain and SPWM technique has been applied to formulate the switching pattern for three level and five level diode clamped inverter that minimize the harmonic distortion at the inverter output. This paper deals with comparison of simulation results of three levels and five level diode clamped inverter.

Keywords: Inverter, Topologies of Multilevel, THD, Sinusoidal Pulse Width Modulation, Waveform, Three level Inverter, Five Level Inverter.

#### I. INTRODUCTION

The power in the battery is in DC mode and the motor that drives the wheels usually uses AC power, therefore there should be a conversion from DC to AC by a power converter. Inverters can do this conversion. The simplest topology that can be used for this conversion is the two-level inverter that consists of four switches. Each switch needs an anti-parallel diode, so there should be also four anti parallel diodes. There are also other topologies for inverters. A multilevel inverter is a power electronic system that synthesizes a sinusoidal voltage output from several DC sources. These DC sources can be fuel cells, solar cells, ultra capacitors, etc. The main idea of multilevel inverters is to have a better sinusoidal voltage and current in the output by using switches in series. Since many switches are put in series the switching angles are important in the multilevel inverters because all of the switches should be switched in such a way that the output voltage and current have low harmonic distortion. The THD will be decreased by increasing the number of levels. It is obvious that an output

Vol. No.4, Issue 07, July 2015

#### www.ijarse.com

IJARSE ISSN 2319 - 8354

voltage with low THD is desirable, but increasing the number of levels needs more hardware, also the control will be more complicated. It is a tradeoff between price, weight, complexity and a very good output voltage with lower THD.

#### II. INVERTER

The DC - AC converter, also known as the inverter, converts dc power to ac power at desired output voltage and frequency. The dc power input to the inverter is obtained from an existing power supply network or from a rotating alternator through a rectifier or a battery, fuel cell, photovoltaic array or magneto hydrodynamic generator. The filter capacitor across the input terminals of the inverter provides a constant dc link voltage. The inverter therefore is an adjustable-frequency voltage source. The configuration of ac to dc converter and dc to ac inverter is called a dc-link converter. Inverters is, referring to the type of the supply source and topology relationship of the power circuit, can be classified as voltage source inverters (VSIs) and current source inverters (CSIs). In this project only the voltage source inverter will be discuss. Furthermore, the power inverter can produce different types of output wave form such as square wave, modified sine wave, and pure sine wave signal. These signal outputs represent different qualities of power output. Square wave inverters result in uneven power delivery that is not efficient for running most devices. Square wave inverters were the first types of inverters made and are obsolete.

#### III. MULTILEVEL INVERTER

Now a day's many industrial applications have begun to require high power. Some appliances in the industries however require medium or low power for their operation. Using a high power source for all industrial loads may prove beneficial to some motors requiring high power, while it may damage the other loads. Some medium voltage motor drives and utility applications require medium voltage. The multi level inverter has been introduced since 1975 as alternative in high power and medium voltage situations. The Multi level inverter is like an inverter and it is used for industrial applications as alternative in high power and medium voltage situations. The need of multilevel converter is to give a high output power from medium voltage source. Sources like batteries, super capacitors, solar panel are medium voltage sources. The multi level inverter consists of several switches. In the multi level inverter the arrangement switches' angles are very important.

#### IV. TOPOLOGY OF MULTILEVEL INVERTER

The basic three types of multilevel topologies used are

- Diode clamped multilevel inverters

- Flying capacitors multilevel inverter or Capacitor clamped multilevel inverter

- Cascaded inverter with separate dc source

#### V. DIODE CLAMPED MULTILEVEL INVERTER

The first invention in multilevel converters was the so-called neutral point clamped inverter. It was initially proposed as a three level inverter. It has been shown that the principle of diode clamping can extended to any

#### www.ijarse.com

IJARSE ISSN 2319 - 8354

level. The main concept of this inverter is to use diodes to limit the power devices voltage stress. The voltage over each capacitor and each switch is  $V_{dc}$ . An n level inverter needs (n-1) voltage sources, 2(n-1) switching devices and (n-1) (n-2) diodes.

As the number of levels increases the harmonic content of the output waveform decreases the filter size.

Lower switching losses due to the devices being switched at the fundamental frequency without increasing the harmonic content in the output. Its Reactive power flow can be controlled, as this does not cause unbalance in the capacitor voltages. It also has fast dynamic response. & in this back to back operation is possible.

But due to high number of clamping diodes is required as the number of levels increase. Its active power transfer causes unbalance in the DC-bus capacitors, this complicates the control of the system.

#### VI. 3-LEVEL DIODE CLAMPED MULTILEVEL INVERTER

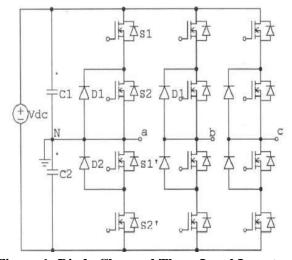

In a 3-level diode clamped multilevel **n=3**so that, its:

Number of switches = 2(n-1) = 4Number of diodes = (n-1)\*(n-2) = 2Number of capacitors = (n-1) = 2

The diode clamped multilevel inverter uses capacitors in series to divide up the DC bus voltage into a set of voltage levels. To produce m levels of the phase voltage, an m level diode clamp inverter needs (m-1) capacitors on the DC bus.

Figure 1: Diode Clamped Three Level Inverters

#### VII. 5 - LEVEL DIODE CLAMPED MULTILEVEL INVERTER

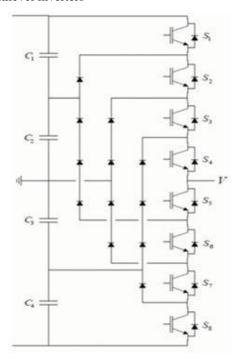

In a 5-level diode clamped multilevel the value for**n**=**5**. Therefore

Number of switches = 2(n-1)=8Number of diodes = (n-1)\*(n-2)=12Number of capacitors = (n-1)=4

Vol. No.4, Issue 07, July 2015

#### www.ijarse.com

IJARSE ISSN 2319 - 8354

A 5-level diode clamped multilevel inverter is shown in Fig. 2. For example to have  $V_{dc}/2$  in the output, switches  $S_1$  to S4 should conduct at the same time. For each voltage level four switches should conduct. As it can be seen in Table.1 the maximum output voltage in the output is half of the DC source. It is a drawback of the diode clamped multilevel inverter. This problem can be solved by using a two times voltage source or cascading two diode clamped multilevel inverters

Figure 2: Diode Clamped five level Inverters

#### VIII. TOTAL HARMONIC DISTORTION (THD)

Power sources act as non-linear loads, drawing a distorted waveform that contains harmonics. These harmonics can cause problems ranging from telephone transmission interference to degradation of conductors and insulating material in motors and transformers. Therefore it is important to gauge the total effect of these harmonics. The summation of all harmonics in a system is known as total harmonic distortion (THD). This paper will attempt to explain the concept of THD and its effects on electrical equipment. It will also outline the low THD of the Associated Power Technologies (APT) line of programmable sources and how these can be used to more effectively test equipment. Total harmonic distortion is a complex and often confusing concept to grasp. However, when broken down into the basic definitions of harmonics and distortion, it becomes much easier to understand

Harmonics have frequencies that are integer multiples of the waveform's fundamental frequency. For example, given a 60Hz fundamental waveform, the 2<sup>nd</sup>, 3<sup>rd</sup>, 4<sup>th</sup> and 5<sup>th</sup> harmonic components will be at 120Hz, 180Hz, 240Hz and 300Hz respectively. Thus, harmonic distortion is the degree to which a waveform deviates from its pure sinusoidalValues as a result of the summation of all these harmonic elements. The ideal sine wave has zero harmonic components. In that case, there is nothing to distort this perfect wave.

Total harmonic distortion, or THD, is the summation of all harmonic components of the voltage or current waveform compared against the fundamental component of the voltage or current wave:

Vol. No.4, Issue 07, July 2015

www.ijarse.com

THD =

$$\frac{\sqrt{(V_2^2 + V_3^2 + V_4^2 + \cdots + V_n^2)}}{V_1} * 100\%$$

The formula above shows the calculation for THD on a voltage signal. The end result is a percentage comparing the harmonic components to the fundamental component of a signal. The higher the percentage, the more distortion that is present on the mains signal

#### IX. SIMULINKMODEL & WAVEFORMS

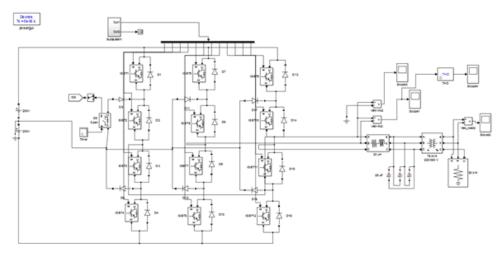

Simulation was carried out to observe the improvement in the line voltage THD and as the inverter level increases from 3-level to 5-level.

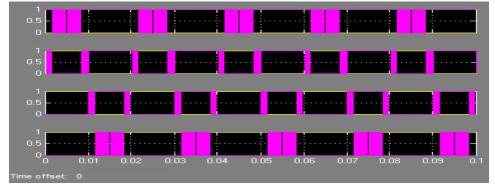

#### 9.1 Simulation Model of Three -Level Dcmli

Figure 3:Three level DCMLI simulation circuit

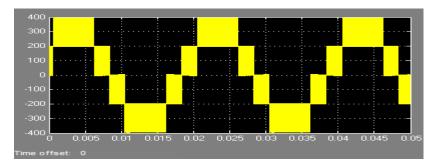

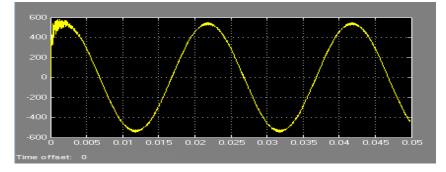

Figure 4: Phase voltage of 3 level DCMLI

Figure 5: output voltage of 3 level DCMLI

Vol. No.4, Issue 07, July 2015

www.ijarse.com

IJARSE ISSN 2319 - 8354

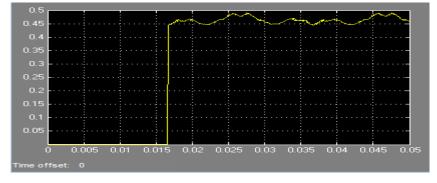

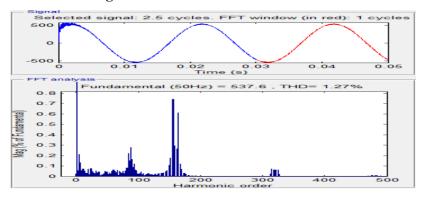

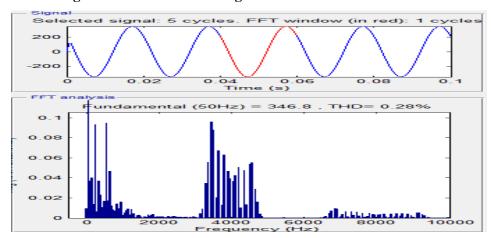

Figure 6:THD level of 3 Level DCMLI

Figure 7: THD Waveform of the output of 3-Level DCMLI

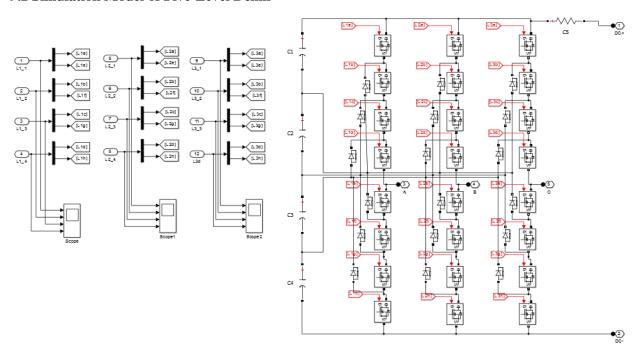

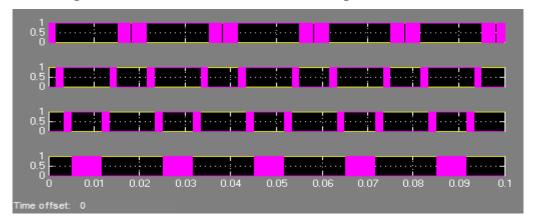

#### 9.2 Simulation Model of Five-Level Dcmli

Figure 8: 5 Level Simulation DCMLI Circuit

Vol. No.4, Issue 07, July 2015

www.ijarse.com

IJARSE ISSN 2319 - 8354

Figure 9:Simulation Waveform of Line Voltage of 5 Level DCMLI

Figure 10: Simulation Voltage Waveform of 5 Level DCMLI

Figure 11: THD Waveform of the Output of 5-level DCMLI

#### X. RESULTS

Simulation was carried out to observe the improvement in the line voltage and THD for RL load as the inverter level increases from 3-level and 5-level which is as shown in the given Table 1.

Vol. No.4, Issue 07, July 2015

www.ijarse.com

#### Table1:Simulation Result for THD of 3 &5 level DCMLI

| Multilevel inverter | Fundamental  | Voltage Level | % of THD |

|---------------------|--------------|---------------|----------|

|                     | Frequency(f) |               |          |

| Three level DCMLI   | 50HZ         | 537.6(V)      | 1.27%    |

| Five level DCMLI    | 50HZ         | 346.89(V)     | 0.28%    |

#### XI. CONCLUSION

In this paper Pulse Width Modulation Technique is applied on diode clamped multilevel inverters and percentage of total harmonic distortions of three and five levels of inverter are simulated and compared. The simulated results are presented in this paper and it is concluded, we can see that in above Table: 1, the % THD of three level inverter is 1.27% at voltage level 537.6(v)& the % THD of five levels is 0.28% at voltage level 346.89(v). When the voltage level is decreases, and no. of level is increases the total harmonic distortion will decreases.

#### **REFRENCES**

- [1] A. K. Gupta and A. M. Khambadkone, "A general space-vector PWM algorithm for multilevel inverters, including operation in over modulation range," IEEE Trans. Power Electron., vol. 22, no. 2, pp. 517–526,Mar. 2007

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral point clamped PWM inverter", ZEEETrans., 1981,1A-17,(5), pp.518-523.

- [3] N. S. Choi, J. G. Cho, and G. H. Cho, "A general circuit topology of multilevel inverter," IEEE PESC'91, 1991, pp. 96–103.

- [4] S., Mishra A., B. Srinivas, "Control of Voltage Source Inverters using PWM/SVPWM for Adjustable Speed Drive Applications", Dept. of ElectricalEngineering, National Institute Of Technology Rourkela, Rourkela - 769008, May 2009

- [5] N. Mohan Teja, R S Ravi Sankar, P. Harsha, V. UmaShankar'A Novel Method of Diode Clamped Multi-Level Inverter using PWM Technique'IJIES

- [6] PSBHIMBHRApower electronics.

- [7] M.RASHID, POWER ELECTRONICS

- [8] G. Laxminarayana<sup>1</sup>,K.pradeep comparative analysis of 3,5&7 level inverter using space vector PWM(IJAREEIE Vol.2 Issue.7,2013)

- [9] Operation and Design of Multilevel InvertersDr. Keith Corzine University of Missouri-Rolla

- [10] C.Boonmee, Y.Kumsuwan, "A Phase- Shifted Carrier- Based PWM Technique For Cascaded H-Bridge Inverters Application In Standalone PV System," IN PROC. IEEE. CONF., SEP. 2012, VOL. 4, PP.

- [11] F.Z.PENG and J.S.Lai, "A Static VAR Generator Using A Staircase Waveform Multilevel Voltage -Source Converter," IN PROC. PCIM/POWER QUALITY, 1994, PP. 58-66. "Power Converter Options For Power System Compatible Mass Transit Systems" 1994, PP. 285-294.