Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

# SYSTEMATIZED ENERGY-SAVING CARRY-SELECT ADDER - A REVIEW

Priyanka Agrawal<sup>1</sup>, Prof. Vijay Yadav<sup>2</sup>, Prof. Rahul Shrivastava<sup>3</sup>

<sup>1</sup>Mtech. Scholar, <sup>2</sup>Guide, <sup>3</sup>Co-Guide Department of Electronics and Communication, LNCT Bhopal (INDIA)

#### **ABSTRACT**

Delay is an important aspect of microprocessor design which is enhancing rapidly. Power consumption and power dissipation are important design constraints that are useful in increasing battery life and maintaining performance. The design of low delay and low-power VLSI architectures require efficient CPU units, which are optimized for the performance parameters, namely, speed and power consumption. Adders often appear in arithmetic logic unit, Intel execution unit and sometimes in the address generation path. Generally adders are the basic components in general purpose microprocessors and digital signal processors. They also resolved other functions such as subtraction, multiplication and division. Hence, improving performance of the digital adder would greatly advance the execution of binary operations inside a circuit compromised of such blocks. The performance of a digital circuit block is gauged by analyzing its power dissipation, layout area and its operating speed. As a consequence, it is to the point that its performance flexibility well for their speed performance. The common form of adder is the ripple-carry adder which consists of n one-bit full adders connected in series. In this way different types of binary adders Ripple carry adder, Carry look-ahead adder, carry select adder and parallel prefix adders has studied. As the name suggest, the carry "ripples" from the least significant bit to the most significant bit.

Keywords- binary adders, carry select adder, Carry look-ahead adder, Ripple carry adder, CMOS, VLSI.

#### I. INTRODUCTION

Speed is one of the major important design objectives in integrated circuit, after that power dissipation is also other. Multiplier-Accumulator (MAC) unit is main building block of DSP (Digital signal processing). MAC unit is responsible for low power and high speed. This is because speed and output are always concerns of DSP system. Due to dynamic growth of portable electronic devices like laptop, calculator, mobile etc., and the low power devices have become very commercial in today world. A VLSI designer plays the challenging role to achieve a high performance digital signal processing system for real-time signal processing. A common MAC unit consists of multipliers and accumulators that contain the sum of the previous consecutive products. The main agenda of this work is to investigate various multiplier and adder architectures which are suitable for implementing Low power, area efficient and high speed MAC unit.

Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

An Arithmetic unit is made up of adder. A complex digital signal processing (DSP) system involves several adders. To improves the performance of a complex DSP system, an efficient adder design essential. A ripple carry adder (RCA) uses a regular design, but the drawback is carry propagation delay (CPD) in this adder. Various methods have been suggested such as Carry look-ahead and carry select (CS) to reduce the CPD of adders.

A designer can make tradeoffs between the two, through the choices in such factors as voltage levels, micro architecture, logic style or gate sizing and seek to find the balance that will comfort the designer's goals. Designers collect information about the consequences of their decisions of making above choices, and circuit designers use models of varying accuracy and speed to help them for see the consequences of their choices. An perfect understanding of the causes and severity of the power dissipation within a chip might influence a designer to make certain tradeoffs between speed and power, but a less accurate understanding might lead to tradeoffs that are worse for overall performance. Clearly how a microchip dissipates power is instrumental to good design. To lessen the energy dissipation, the circuit activity is looked important. "Arithmetic optimization using carry-save-adders", Carry-save-adder (CSA), well known from multiplier architectures, can be used for the efficient CMOS implementation of a much wider variety of algorithms for high-speed digital signal processing than multiplication. Carry save adders has efficient concepts for implementation of high speed. Furthermore, the requirement of more optimum adder designs for a modern microprocessors initiated in this research. For the applications such as the RISC processor design, where single cycle execution of instructions is the key measure of performance of the circuits, use of an efficient adder circuit becomes necessary, to realize efficient system performance. Additionally, the area is an essential factor which is to be taken into account in the design of fast adders. Towards this end, high-speed, low power and area efficient addition and multiplication have always been a fundamental requirement of high-performance processors and systems. The major speed limitation of adders arises from the huge carry propagation delay encountered in the conventional adder circuits, such as ripple carry adder and carry save adder.

#### II. CONVENTIONAL ADDITION

## 2.1 Serial Addition

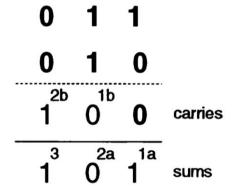

It is common method which we familiar very well. This method is using the binary numbers results in fast algorithm used in mechanical addition. This algorithm was described using Boolean algebra by Shannon [8]. Figure 2.1 shows the operation is taking place between the two three bit operands. The operands are 3 (011) added to 2 (010) to yield 5 (101). The operands are in large bold number. The carry values are represented below the dotted line. The dotted line is used to mark that the carries are generated separately from the original operands, but that they are still added in as though they form a third operand. The solid line separates the sum from the carries. The addition start from the least significant bit to the most significant bit. The serial addition contains a parallel component since both sums and carries are generated simultaneously in each column.

Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

Figure 2.1 Serial Additions Algorithm.

Although, the algorithm is serial in the sense that the columns are processed sequentially starting from the right. The serial steps in figure 2.1 are numbered consecutively, while letters are used to distinguish among the steps that may occur in parallel or in any other order.

## 2.2 Ripple Carry Addition

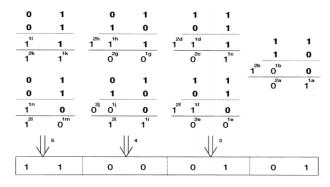

The main difference between the ripple carry addition and serial addition is that ripple carry addition is asynchronous while serial addition is synchronous. In ripple carry addition all of the rectangular style carry chains start simultaneously, as shown for the example case in figure 3.2. Signals in the ripple carry adder can transition multiple times 1 due to the overlapping calculations. The wavering is denoted in the example with crossed out bits.

Figure 2.2 shows the prime events for an example add: the generation of two carries, the carries propagating across the adder, and then later one path running over the other in the upper four bits. More clearly, assuming that when adder starts with all zero carries, the first step in the algorithm comes with the sums in columns 0 and 3, and the carries for columns 1 and 4.

| 5              | 4                   | 3                | 2               | 1               | 0 columns    |

|----------------|---------------------|------------------|-----------------|-----------------|--------------|

| 0              | 1                   | 1                | 1               | 1               | 1 operands   |

| 0              | 1                   | 0                | 1               | 1               | 0            |

| 2d<br><b>1</b> | Ø 1 <sup>d 4b</sup> | Ø1 <sup>3b</sup> | 1 <sup>2b</sup> | 0 <sup>1b</sup> | 0 carries    |

| 13             | Ø 1                 | 1 0 4a           | 1 <sup>3a</sup> | 0 <sup>2a</sup> | 1a<br>1 sums |

Figure 2.2 Ripple carry Addition Algorithm.

#### 2.3 Carry Select Addition

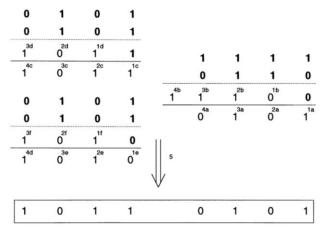

This method is based on the divide and conquer phenomenon, which protects itself against making the wrong choices on the outcome of intermediate carries. To improve the speed of addition, the length of ripple propagate chains must be reduced. Carry would always be zero by the assumptions of any particular point, then the adder could be broken at that point into separate parallel processes, and the sum could be completed early. However, the assumption would be wrong 50% of the time can hedge bets on the outcome of such a carry calculation by starting two upper half adds, each with a different assumption about the value of the particular carry-out. Figure

Vol. No.6, Issue No. 05, May 2017

## www.ijarse.com

3.3 shows an example of adding 01011111 to 01010110. The upper four bits of the add is replicated, the top version has the carry input bit set, while the bottom version does not have the carry bit set. Six items are calculated simultaneously in the first serial step. These contain the first column sum bits in each of the three additions, and the first column carry-out bits. Independently, these three additions continue on as in ripple carry addition till the carry proceed from the least significant four bits lead to the selection of the correct upper four bits, 1011 in the last step. This carry select addition requires only five serially dependent steps to add 8 bit operands in contrast to ripple carry addition of the same length operands would require 8 serially dependent steps.

The carry select algorithm is as follows:

- (A). Conduct the three ripple carry adds simultaneously:

- i. One adds with the lower half bits.

- ii. Two adds with the upper half bits.

- One with the carry-in set to one.

- One with the carry-in set to zero.

- (B). Take in the correct upper half.

However, the number of series steps for conducting this type of addition is approximately half the number for ripple carry addition, constant factors do not change the order of growth, and the performance is still linear:

Figure 2.3 Carry Select Addition Algorithm.

## 2.4 Ripple Carry Select.

Carry select method divide the number into two segment but ripple carry addition is made by breaking into a large number of segment.

Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

Figure 2.4 A ripple Carry Addition algorithm.

For instance, From the previous example, the 8 bit addition can be broken into four 2 bit segment, as shown in figure 2.4. Each of the 2 bit segment include duplicated 2 bit adders: one copy adds with an assumed carry-in of one, and the other with an assumed carry-in of zero. The right segment are selected in ripple fashion: the bottom 2 bit add selects among the right second section add, and the right second section add then provides the right carry for the third section, which provides the right carry for the fourth section.

## III. PRIOR WORK

B. K. Mohanty and S. K. Patel,[1] In this brief, the logic operations involved in conventional carry select adder (CSLA) and binary to excess-1 converter (BEC)-based CSLA are analyzed to study the data dependence and to identify redundant logic operations. We have eliminated all the redundant logic operations present in the conventional CSLA and proposed a new logic formulation for CSLA. In the proposed scheme, the carry select (CS) operation is scheduled before the calculation of-final-sum, which is different from the conventional approach. Bit patterns of two anticipating carry words (corresponding to cin = 0 and 1) and fixed cin bits are used for logic optimization of CS and generation units. An efficient CSLA design is obtained using optimized logic units. The proposed CSLA design involves significantly less area and delay than the recently proposed BEC-based CSLA. Due to the small carry-output delay, the proposed CSLA design is a good candidate for square-root (SQRT) CSLA. A theoretical estimate shows that the proposed SQRT-CSLA involves nearly 35% less area-delay-product (ADP) than the BEC-based SQRT-CSLA, which is best among the existing SQRT-CSLA designs, on average, for different bit-widths. The application-specified integrated circuit (ASIC) synthesis result shows that the BEC-based SQRT-CSLA design involves 48% more ADP and consumes 50% more energy than the proposed SQRT-CSLA, on average, for different bit-widths.

L. Mugilvannan and S. Ramasamy,[2] Carry Select Adder (CSLA) is one of the fastest adders used in many data-processing processors to perform fast arithmetic functions. From the structure of the CSLA, it is clear that there is scope for reducing the area and power consumption in the CSLA. This work uses a simple and efficient transistorlevel modification in BEC-1 converter to significantly reduce the area and power of the CSLA. Based on this modification 16-b square-root CSLA (SQRT CSLA) architecture have been developed and compared with the SQRT CSLA architecture using ordinary BEC-1 converter. The proposed design has reduced area and power as compared with the SQRT CSLA using ordinary BEC-1 converter with only a slight increase in the delay. This work evaluates the performance of the proposed designs in terms of delay, area, and power by hand

Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

with logical effort and through Cadence Virtuoso. The results analysis shows that the proposed CSLA structure is better than the SQRT CSLA with ordinary BEC-1 converter.

L. Suri, D. Lamba, K. Kritarth and G. Sharma,[3] Highly-increasing requirement for mobile and several electronic devices want the use of VLSI circuits which are highly power efficient. The most primitive arithmetic operation in processors is addition and the adder is the most highly used arithmetic component of the processor. Carry Select Adder (CSA) is one of the fastest adders and the structure of the CSA shows that there is a possibility for increasing its efficiency by reducing the power dissipation and area in the CSA. This research work presents power and delay analysis of various adders and proposed a 32-bit CSA that is implemented using Hybrid PTL/CMOS logic style. This work evaluates and analyses the performance of the proposed designs in terms of area, delay, power, and their products in 90nm CMOS process technology. The results analysis is showing that the proposed CSA structure shows better result in terms of area, power and PDP (Power Delay Product) than the others.

A. Grover and N. Grover, [4] This article proposed an area-efficient carry select adder by sharing the common Boolean logic term. Representation of the circuit in summation operation need one XOR gate and one Inverter, while carry out can be represented using one AND gate and an inverter. Using the multiplexer, we are able to select the correct output results according to the carry input signal. In this way, the transistor count in a 32-bit carry select adder can be greatly reduced from 1947 to 960 and the carry select adder performs with a faster speed as compare to the carry ripple adder. Two different design styles using one multiplexer and two multiplexers has also been considered in terms of number of transistors, average power consumption, propagation delay at sum and at carry output.

A. Ramakrishna Reddy and M. Parvathi,[5] Most of the VLSI applications, such as DSP, image and video processing, and microprocessors use carry select adder (CSLA) for arithmetic functions. From the structure of regular SQRT CSLA, still there is possibility to obtain better design in which optimization of area, power are to be major concentrations along with high speed performance. One of the existing solutions used in SQRT CSLA is replacement of second level RCA by BEC. Though increases the performance, very less percentage of improvement in reduction of area and power dissipation. And also the existing adder with BEC technique is not suitable for low power applications. Hence this work proposes Special Hardware using Multiplexers (SHM) design in place of second level RCA. It is observed from the results that the area and power dissipation are reduced at comparable percentages with respect to the RCA and BEC techniques. When SHM is used at the second level of second block in 16-bit SQRT CSLA, observed that area is reduced by 13.5% and power dissipation is reduced by 6.4%. This proposed logic is designed in transistor level using 0.12μm technology in the Micro wind tool.

M. A. Akbar and J. A. Lee, [6] The common design problem in various approaches for self-checking adders is the fault propagation due to carry. Such a fault can misguide the system to detect the particular faulty module. In this work, we proposed a self-checking Carry Select Adder (CSA) with fault localization ability. Our scheme can provide minimum area overhead for self-recovery process because instead of replacing the whole system we can now replace the particular faulty modules. The proposed self-checking CSA consumes 12% less area with equal performance as compared to the previously proposed self-checking CSA approach.

Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

S. Parmar and K. P. Singh,[7] The work describes the power and area efficient carry select adder (CSA). Firstly, CSA is one of the fastest adders used in many data-processing systems to perform fast arithmetic operations. Secondly, CSA is intermediate between small areas but longer delay Ripple Carry Adder (RCA) and a larger area with shorter delay carry look-ahead adder. Third, there is still scope to reduce area in CSA by introduction of some add-one scheme. In Modified Carry Select Adder (MCSA) design, single RCA and BEC are used instead of dual RCAs to reduce area and power consumption with small speed penalty. The reason for area reduction is that, the number of logic gates used to design a BEC is less than the number of logic gates used for a RCA design. Thus, importance of BEC logic comes from the large silicon area reduction when designing MCSA for large number of bits. MCSA architectures are designed for 8-bit, 16-bit, 32-bit and 64-bit respectively. The design has been synthesized at 90nm process technology targeting using Xilinx Spartan-3 device. Comparison results of modified CSA with conventional CSA show better results and improvements.

#### IV. PROBLEM STATEMENT

In a microprocessor or a digital signal processor (DSP), data path plays a prominent role since performance metrics like the die-area, speed of operation, power dissipation etc., depend directly on the efficiency of datapath. As is known, core of the data path involves complex computations like addition, subtraction, multiplication and division, etc. Thus, realizing efficient hardware units for these computations, which directly affect the performance of data path, is of prime importance. The most executed operation in the data path is addition, which requires a binary adder that adds two given numbers. Adders also play a vital role in more complex computations like multiplication, division and decimal operations. Hence, an efficient implementation of binary adder is crucial to an efficient data path. Relatively significant work has been done in proposing and realizing efficient adder circuits for binary addition.

## V. CONCLUSION

For development of efficient adder architectures that address the problems of high fan-out, delay and power consumption. These architectures while having a delay overhead have the advantage of relatively small fan-out and reduced energy consumption overall. Various literature and different algorithms of binary addition like serial addition ripple carry addition carry select addition and ripple carry addition are reviewed. The ripple carry adder is most popular among all the delay of carry select adder and carry look ahead adder is considerably less compared to ripple carry adders. Some new algorithms are also discussed. The need to identify optimum adder designs for a modern microprocessor initiated this study. Adders often appear in the integer execution unit, and sometimes in the address generation path. If a floating-point unit is present they appear in the significant adder, at the base of multiplier array, and in the divider. Smaller adders appear in the exponent manipulation circuitry for multiply and divide.

Vol. No.6, Issue No. 05, May 2017 www.ijarse.com

#### **REFERENCES**

- [1] B. K. Mohanty and S. K. Patel, "Area–Delay–Power Efficient Carry-Select Adder," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 61, no. 6, pp. 418-422, June 2014.

- [2] L. Mugilvannan and S. Ramasamy, "Low-power and area-efficient carry select adder using modified BEC-1 converter," 2013 Fourth International Conference on Computing, Communications and Networking Technologies (ICCCNT), Tiruchengode, 2013, pp. 1-5.

- [3] L. Suri, D. Lamba, K. Kritarth and G. Sharma, "High performance and power efficient 32-bit carry select adder using hybrid PTL/CMOS logic style," 2013 International Mutli-Conference on Automation, Computing, Communication, Control and Compressed Sensing (iMac4s), Kottayam, 2013, pp. 765-768.

- [4] A. Grover and N. Grover, "Comparative Analysis: Area-Efficient Carry Select Adders 180 Nm Technology," 2013 7th Asia Modelling Symposium, Hong Kong, 2013, pp. 99-102.

- [5] A. Ramakrishna Reddy and M. Parvathi, "Efficient carry select adder using 0.12μm technology for low power applications," 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), Mysore, 2013, pp. 550-553.

- [6] M. A. Akbar and J. A. Lee, "Self-Checking Carry Select Adder with Fault Localization," 2013 Euromicro Conference on Digital System Design, Los Alamitos, CA, 2013, pp. 863-869.

- [7] S. Parmar and K. P. Singh, "Design of high speed hybrid carry select adder," 2013 3rd IEEE International Advance Computing Conference (IACC), Ghaziabad, 2013, pp. 1656-1663.

- [8] N. Sloane and A. D. Wyner, eds., Claude Elwood Shannon Collected Works. IEEE Press, 1993. [1] Y. He, C. H. Chang, and J. Gu, "An area-efficient 64-bit square root carry- select adder for low power application," in Proc. IEEE Int. Symp. Circuits Syst., 2005, vol. 4, pp. 4082-4085.

- [9] B. Ramkumar and H. M. Kittur, "Low-power and area-efficient carry-select adder," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371-375, Feb. 2012.

- [10] I.-C. Wey, C.-C. Ho, Y.-S. Lin, and C. C. Peng, "An area-efficient carry select adder design by sharing the common Boolean logic term," in Proc. IMECS, 2012, pp. 1-4.

- [11] S. Manju and V. Sornagopal, "An efficient SQRT architecture of carry select adder design by common Boolean logic," in Proc. VLSI ICEVENT, 2013, pp. 1-5.

- [12] B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs, 2nd ed. New York, NY, USA: Oxford Univ. Press, 2010.